Services

Architecture and Design Expertise

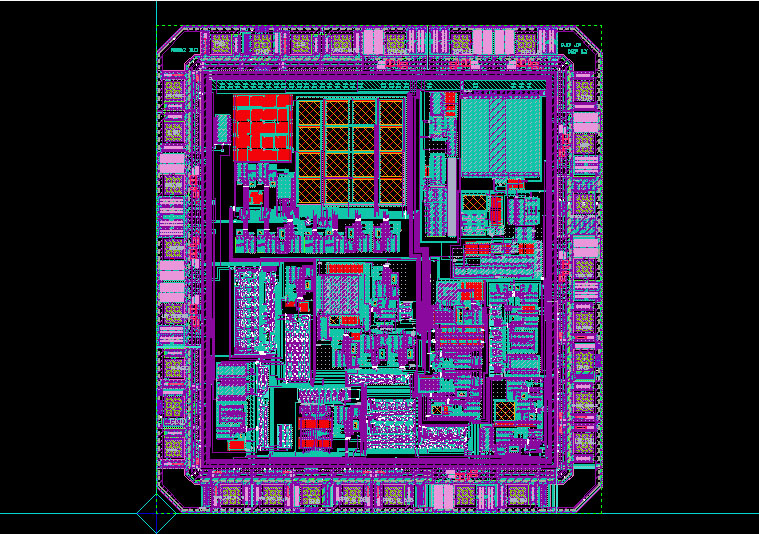

We are well established semiconductor design company in India. Digicomm Semiconductor has developed expertise as a young semiconductor solutions provider making it one of the best semiconductors service company around implementing complex algorithmic designs. Our designed semiconductor has made us one of the best semiconductor company in India.

-

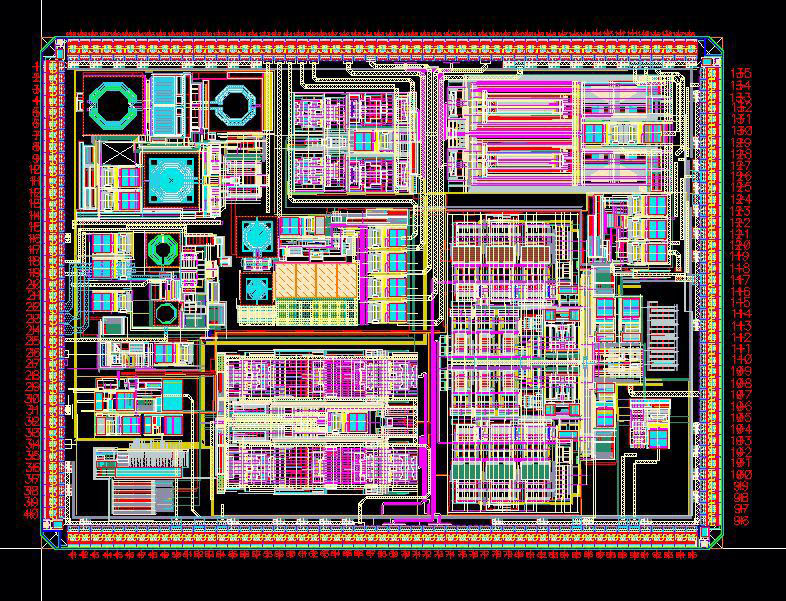

uArch Specification to Net list

uArch Specification to Net list

-

Chip planning, interface details and detailed micro architecture for all PD modules.

Chip planning, interface details and detailed micro architecture for all PD modules.

-

Experience in leading and implementing complex algorithmic designs.

Experience in leading and implementing complex algorithmic designs.

-

Designed chip up to 16FF technology with more than 12M instances and up to 512Mb embedded memory.

Designed chip up to 16FF technology with more than 12M instances and up to 512Mb embedded memory.

-

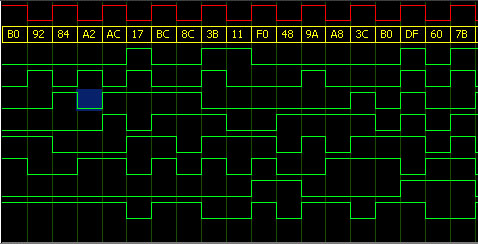

Experience in designing for timing closure friendly for speed up to 1.2GHz.

Experience in designing for timing closure friendly for speed up to 1.2GHz.

-

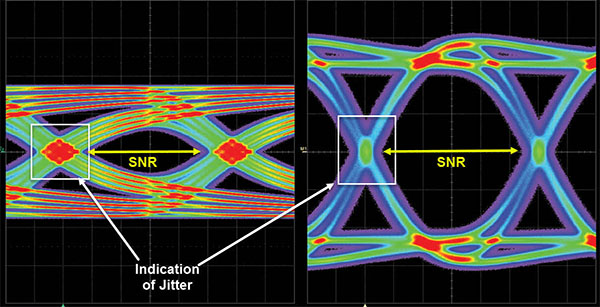

Ethernet and Interlaken Phy and MAC designs.

Ethernet and Interlaken Phy and MAC designs.

-

PCIe implementation up to Gen4 and 16-lanes supporting 1, 2 or 4 ports

PCIe implementation up to Gen4 and 16-lanes supporting 1, 2 or 4 ports

-

Up to 48 56G PAM4 serdes integration.

Up to 48 56G PAM4 serdes integration.

-

AVS and power islands for power saving.

AVS and power islands for power saving.

Floor planning

Floor planning